СТРУКТУРА ПАМЯТИ

Блок памяти состоит, как правило, из ОЗУ и ПЗУ. В ОЗУ и ПЗУ хранятся данные и программы пользователя. В ПЗУ помешаются те данные и программы, которые должны сохраняться при выключении питания. Во-первых, в ячейки ОЗУ информация может попадать, в результате работы какой-либо программы, во-вторых, пользователь может сам изменить их содержание при помощи клавиатуры.

Максимальное количество ячеек памяти (или "объем памяти"), к которым может обращаться при помощи своей 16-разрядной шины адреса микропроцессор КР580ИК80А, равно 216, или 65 536. Обычно говорят: не 65 536 ячеек, а 64 К (1 К равняется 1024). Для решения некоторых задач оказывается мало и такого объема памяти, но для большинства применений достаточно использовать лишь его часть. С другой стороны, объем памяти, содержащейся в одной микросхеме, может быть меньше, чем максимальный объем, который может адресовать микропроцессор. Эти два обстоятельства, а также и то, что в составе памяти микро-ЭВМ необходимо иметь память с разными свойствами (ОЗУ и ПЗУ), приводят к специальным техническим решениям при конструировании памяти микро-ЭВМ.

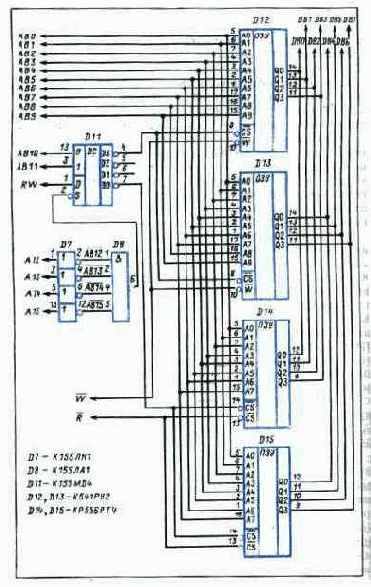

Рассмотрим эти технические решения на примере блока памяти ПМ-ЭВМ. Блок памяти, состоящий из двух микросхем ОЗУ и двух ПЗУ, подключается к шинам данных, адреса и управления (рис. 7.1). В качестве ОЗУ в ПМ-ЭВМ используются микросхемы статической памяти КР541РУ2 (см. гл. 4) с организацией 1024x4 бита. Поэтому для получения объема памяти 1 Кбайт (1024 байта) необходимо подключить две микросхемы, присоединив выводы данных одной микросхемы (D12) к линиям DBO-DB3 шины данных, а выводы другой (D13) — к линиям DB4 — DB7. Остальные выводы микросхем D12 и D13 подключаются к одним и тем же линиям. Таким образом составляется блок ОЗУ емкостью 1 Кбайт.

В качестве ПЗУ в ПМ-ЭВМ используются две микросхемы КР556РТ4 (D14, D15) с организацией 256x4 бит. Они включены аналогично микросхемам ОЗУ, т. е. организованы в блок 25 6 байтов.

Рис. 7.1. Схема блока памяти

Теперь рассмотрим, как размещается блок ОЗУ объемом 1 Кбайт и блок ПЗУ объемом 256 байт в пространстве адресов, вырабатываемых микропроцессором. Для того чтобы осуществить привязку блоков ОЗУ и ПЗУ, старшие разряды адреса (линии АВ10-АВ15) подаются на схему дешифрации адреса (микросхемы D8, D11, рис. 7.1). Шесть старших разрядов адреса АВ10-АВ15 определяют, к какому килобайту памяти микропроцессора будет произведено обращение. Десять младших разрядов адреса АВО-АВ9 адресуют байты памяти в пределах каждого килобайта. Каждому коду на АВ10-АВ15 соответствует один килобайт памяти, но вследствие того, что инвертированные линии АВ12-АВ15 шины адреса поступают на микросхему D8, сигнал с выхода которой разрешает или запрещает работу дешифратора D11, дешифратор D11 будет работать только при нулевых кодах на этих линиях. В зависимости от кода на линиях АВ10 — АВ15 низкий уровень будет появляться на одном из выходов 7, 6, 5 или 4 дешифратора D11 при условии, что на втором управляющем входе дешифратора (вывод 1) будет высокий уровень. В табл. 7.1 дается соответствие кода на линиях АВ 10 — АВ 15 номеру вывода D11.

В табл. 7.1 приводятся адрес первого байта, адрес последнего байта и условный номер килобайта памяти, к которому происходит обращение при определенном коде на линиях АВ10 — АВ15. Из пятой строки табл. 7.1 также видно, что если адрес, вырабатываемый микропроцессором, лежит в диапазоне от 010000Q до 177 OOOQ, то ни на одном из выходов дешифратора не будет низкого уровня, т. е. с помощью выходов этого дешифратора нельзя адресоваться к килобайтам с 4-го по 63-й.

Выходы дешифратора используются для привязки отдельных блоков памяти емкостью 1 Кбайт к определенным областям в пространстве адресов микропроцессора; для этого они соединены со входами микросхемы памяти, разрешающими их работу, а на адресные входы микросхемы памяти подаются младшие разряды адреса, которые осуществляют адресацию ячеек памяти внутри микросхем.

Таблица 7.1

|

Код на линиях АВ10— АВ1 5 |

Номер вывода D11.на котором низкий уровень напряжения |

Диапазон адресов области памяти в восьмеричном коде |

Номер адресуемого ки- |

||||||

|

А15 |

А14 |

А13 |

А12 |

All |

А10 |

|

от адреса |

до адреса |

лобайта |

|

0 |

0 |

0 |

0 |

0 |

0 |

7 |

000 000 |

001 777 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

6 |

002 000 |

003 777 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

5 |

004000 |

005 777 |

2 |

|

0 |

0 |

0 |

0 |

1 |

1 |

4 |

006 000 |

007 777 |

3 |

|

Любой другой код |

|

|

- |

010 000 |

177777 |

4-63 |

Блок из микросхем ПЗУ подключен так, что он занимает самые младшие адреса, начиная с 000 000Q. Это сделано для размещения программы-монитора, которая должна начинать работать сразу после включения микро-ЭВМ, или нажатия кнопки СБРОС, в результате чего вырабатывается сигнал RESET, по которому микропроцессор начинает выполнять команду, расположенную по адресу 000 OOOQ (т. е. в ПЗУ). Заметим,что для адресации 256 байтов ПЗУ достаточно восьми адресных линий ABO — AB7; линии АВ8, АВ9 излишни и поэтому к ПЗУ не подсоединены. В результате этого независимо от кода на линиях АВ8 и АВ9 адресуется байт ПЗУ, определяемый адресом на линиях ABO — AB7. Это приводит к тому, что один и тот же байт ПЗУ можно считывать по адресам, в разрядах АВ8, АВ9 которых находятся коды 00, 01, 10 или 11. Область памяти ПЗУ, состоящая из 256 байт, повторяется 4 раза в нулевом килобайте памяти. Ясно, что это повторение не мешает работе микропроцессора.

Такая схема адресации с неиспользованием части разрядов адреса называется схемой с неполной дешифрацией адреса. При необходимости использовать весь нулевой килобайт и поместить в пространство его адресов еще три блока памяти по 256 байт в каждом нужно использовать для разрядов АВ8 и АВ9 полный дешифратор, устроенный так же, как для разрядов АВ10 и АВ11. Схема с неполной дешифрацией адреса приводит к тому, что используется не все адресное пространство, но зато требуется меньше микросхем для ее реализации, и поэтому такая схема часто применяется в простых микро-ЭВМ.

Блок из микросхем ОЗУ подключен к выходу 4 дешифратора D11, и поэтому килобайт ОЗУ адресуется как 3-й килобайт в адресном пространстве микропроцессора. На рис. 7.2 приведена карта распределения памяти в ПМ-ЭВМ.

Этого объема памяти достаточно для нормальной работы, но его можно при необходимости увеличить. Объем используемого ОЗУ можно увеличить до 3 Кбайт, ничего не переделывая в схеме дешифрации адреса, а просто подключением дополнительных блоков ОЗУ емкостью по 1 Кбайт к выходам 6 и 5 дешифратора D11 (рис. 7.1). Можно также увеличить объем используемого ПЗУ, если построить его из микросхем большей емкости, например из микросхем К573РФ1 с организацией 1024x8 бит (1 Кбайт) или микросхем КР556РТ5 емкостью 4 Кбита и с организацией 512x8 бит (0,5 Кбайта). В первом случае будет использоваться весь 0-й килобайт, а во 2-м ячейки ПЗУ будут повторяться во второй половине 0-го килобайта.

|

|

|

|

|

000 000 |

|

|

|

|

ПЗУ |

|

|

000 377 |

|

|

|

000 400 000 777 |

Повторяется ПЗУ |

|

|

001 000 001 377 |

Повторяется ПЗУ |

0 и К баит |

|

001 400 001 777 |

Повторятся ЛЗУ |

|

|

002 000 |

|

|

|

|

Память |

|

|

|

отсутствует |

1-й К байт |

|

003 777 |

|

|

|

004 000 |

|

|

|

|

Память |

|

|

|

отсутствует |

2-й K бaйm |

|

005 777 |

|

|

|

005 000 |

|

|

|

|

ОЗУ |

3-й K бaйm |

|

|

Область стека |

|

|

007 777 |

|

|

Осталось рассмотреть подключение блока памяти к линиям шины управления. Линия R (рис. 7.1) подключена к входам 13 микросхем ПЗУ и разрешает их работу во время цикла считывания байта из ПЗУ. Линия W подключена к входам 10 микросхем ОЗУ и управляет записью байта в ОЗУ. Если на ней во время цикла обращения к ОЗУ поддерживается высокий уровень, то происходит считывание, а если низкий - то запись байта. Сигнал RW, вырабатывающийся и сигналом R, и сигналом W, служит Для того, чтобы разрешать работу дешифратора D11 только во время низкого уровня сигналов R и W.

Это необходимо, чтобы считывание и запись в блок памяти происходили во время выра ботки сигналов R и W, которые формируются сигналами DBIN и WR микропроцессора, определяющими момент передачи информации по шине данных.

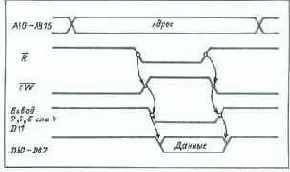

Рис. 7.3. Временная диаграмма работы блока памяти при чтении

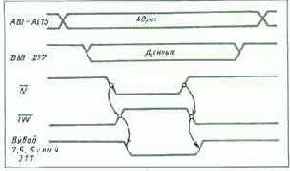

Рис. 7.4. Временная диаграмма работы блока памяти при записи

Считывание из ОЗУ микропроцессор может выполнить в циклах ВЫБОРКА КОМАНДУ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА а считывание из ПЗУ - только в циклах ВЫБОРКА КОМАНДЫ И ЧТЕНИЕ ИЗ ПАМЯТИ. Временные диаграммы сигналов шины адреса, данных и управления приведены на рис. 7.3. Запись информации в ОЗУ микропроцессор может выполнить в циклах ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК. Временные диаграммы записи приведены на рис. 7.4.