ШИНЫ АДРЕСА, ДАННЫХ И УПРАВЛЕНИЯ

Шина адреса. Микропроцессор КР580ИК80А имеет 16-разрядную шину адреса А0-А15. Эта шина выполняет две функции. Первая функция состоит в передаче адреса ячейки памяти (стека) при обращении к памяти (стеку). С помощью 16 разрядов шины адреса можно адресовать 216 ячеек памяти (т. е. 64 Кбайта). Вторая функция шины адреса — это передача адреса внешнего устройства при выполнении команд IN и OUT. В этом случае адрес внешнего устройства появляется на линиях АО-А7 и дублируется на линиях А8-А15. Так как для передачи адреса внешнего устройства используется фактически только восемь разрядов, то можно адресовать 256 (2s) различных внешних устройств ввода/вывода.

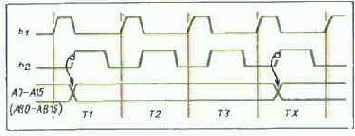

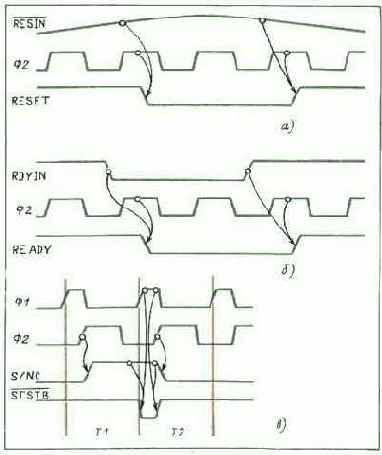

Временная диаграмма работы шины адреса приведена на рис. 6.3. Адрес появляется на шине по фронту сигнала Ф2 в такте Т1 и поддерживается три такта до фронта сигнала Ф2 в такте ТХ. Такт ТХ может быть четвертым тактом (Т4) машинного цикла, если цикл имеет более трех тактов, и может быть тактом Т1 следующего машинного цикла, если данный цикл имеет три такта.

Рис. 6.3. Временная анаграмма работы шины адреса

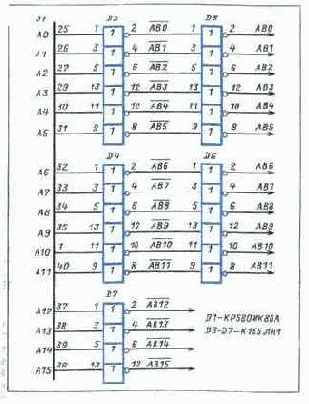

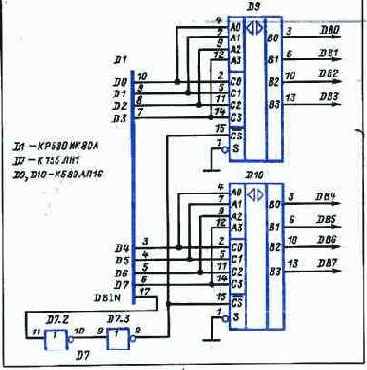

Каждая линия шины адреса является ТТЛ-выходом с тремя состояниями и нагрузочной способностью, равной единице. Так как шину адреса необходимо подавать на многие блоки ПМ-ЭВМ, то необходимо буферизовать ее линии, т. е. увеличить их нагрузочную способность. Для этого каждая линия подключается к входу схемы, состоящей из двух последовательно включенных инверторов (рис. 6.4). В результате на выходе второго инвертора имеется сигнал такого же уровня, как и на входе первого, но выход инвертора микросхемы К155ЛН1 имеет нагрузочную способность, равную 10.

Шина данных. Микропроцессор КР580ИК80А имеет 8-разрядную двунаправленную шину данных DO — D7. Шина данных выполняет две функции. Первая функция — передача управляющего слова, вторая — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Шина данных — единственная двунаправленная шина микропроцессора. Ее выходы также являются выходами с тремя состояниями.

Рассмотрим функцию передачи управляющего слова. Известно (см. § 6.2), что микропроцессор КР580ИК80А имеет 10 типов машинных циклов. Информация о том, какого типа цикл будет выполняться, передается в начале каждого цикла по линиям шины данных и называется управляющим словом. Все управляющие слова перечислены в табл. 6.2. Управляющее слово или только его часть можно запомнить с помощью дополнительных триггеров и использовать затем для формирования сигналов шины управления. Как это делается, будет описано ниже.

Рис. 6.4. Шина адреса

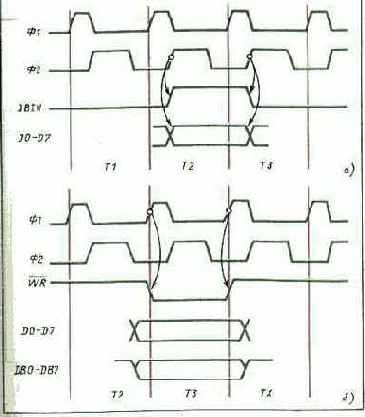

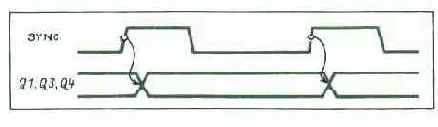

Для того чтобы показать, что идет процесс передачи управляющего слова, используется выход микропроцессора SYNC. Временная диаграмма приводится на рис. 6.5. Из нее видно, что передача управляющего слова по шине данных начинается по фронту сигнала Ф2 в такте Т1 и заканчивается по тому же фронту сигнала Ф2 в такте Т2.

Рис. 6.5. Временная диаграмма процесса передачи управляющего слова

Рассмотрим вторую функцию шины данных — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Во время циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА, ВВОД С ВНЕШНЕГО УСТРОЙСТВА, ПРЕРЫВАНИЕ информация передается по шине данных в один из внутренних регистров микропроцессора из какого-либо блока микро-ЭВМ, а во время циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК, ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО - из внутреннего регистра в какой-либо блок.

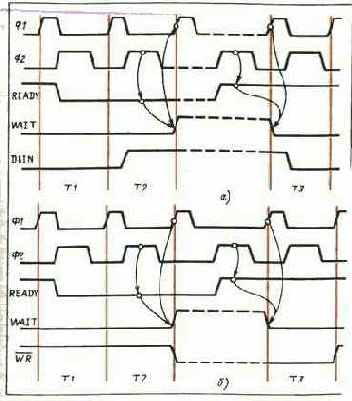

Для указания направления передачи информации по шине данных микропроцессор имеет два выхода: DBIN и WR. Когда информация передается в микропроцессор, то в этом машинном цикле на выходе DBIN появляется высокий уровень (рис. 6.6,а). Сигнал DBIN появляется по фронту сигнала Ф2 в такте Т2 и снимается по фронту Ф2 в такте ТЗ. Именно в это время внешние схемы должны поместить на шину данных код, который должен быть записан в один из внутренних регистров. Когда информация передается из микропроцессора, то в этом машинном цикле вырабатывается сигнал WR низкого уровня (рис. 6.6,6). Этот сигнал вырабатывается по фронту сигнала Ф1 в такте Т2 и снимается по фронту Ф1 в такте Т4 этого же машинного цикла (если цикл состоит более чем из трех тактов) или в такте Т1 следующего машинного цикла (если данный цикл состоит из трех тактов).

На шине данных ЕЮ — D7 немного ранее появления сигнала WR микропроцессор помещает данные и снимает их позднее снятия сигнала WR, поэтому внешние схемы могут использовать этот сигнал для управления записью информации.

Рис. 6.6. Временная диаграмма работы шины данных

Каждая линия шины данных имеет единичную нагрузочную способность и поэтому нуждается в буферизации. Поскольку линии шины данных двунаправленны, необходим и двунаправленный буфер. Схема такого буфера, состоящая из двух микросхем К589АП16 (D9, D10), приводится на рис. 6.7. На входы 1 микросхем D9, D10 подан низкий уровень, и поэтому они работают все время в режиме передачи информации. Направление передачи определяется уровнем буферизованного сигнала DBIN, который подключен к входам 15 микросхем D9, D10. 3аметим, что направление передачи не управляется сигналами WR и SYNC .

Если уровень сигнала DBIN высокий, то шинные формирователи передают информацию в направлении к микропроцессору (от DBO — DB7 к DO — D7), если нет — то в обратном направлении (от ЕЮ — D7 к DBO — DB7), т. е. направление передачи шинных формирователей при низком уровне сигнала DBIN соответствует тому, которое должно быть при выработке сигналов WR и SYNC.

Рис. 6.7. Шина данных

Рис. 6.8. Шина управления

Шина управления. Микропроцессор КР580ИК80А не обладает готовой шиной управления, как шиной адреса и шиной данных. Поэтому эта шина организуется с помощью дополнительной внешней схемы (микросхемы D27, D29), называемой иногда системным контроллером (СК), которая использует управляющее слово и управляющие сигналы микропроцессора (рис. 6.8). Часть разрядов управляющего слова (D4, D6, D7) фиксируется в триггерах микросхемы К155ТМ7 (D29) по срезу сигнала SYNC (рис. 6.9). Сигнал SYNC пропущен через два инвертора для увеличения нагрузочной способности (эта схема, хотя и работоспособна, не будет применяться в ПМ-ЭВМ). Позднее будет приведена схема для фиксации управляющего слова, где сигнал на управляющие входы триггеров будет вырабатываться с помощью микросхемы КР580ГФ24.

Сигналы шины управления вырабатываются с помощью сигналов с выходов триггеров микросхем D29 и сигналов DBIN и WR.

Рис. 6.9. Временная диаграмма работы фиксаторов управляющего слова

В ПМ-ЭВМ команды, данные и содержимое стека хранятся в едином блоке памяти, состоящем из ОЗУ и ПЗУ. Поэтому Для управления чтением из блока достаточно иметь один сигнал R, который будет вырабатываться при выполнении машинных циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА. Назовем условно эту группу циклов ЧТЕНИЕ. Для управления записью в блок также достаточно иметь один сигнал W, который будет вырабатываться при выполнении машинных циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК. Эту группу назовем ЗАПИСЬ.

Для управления вводом и выводом на внешние устройства необходимы два сигнала OUT и IN, которые будут вырабатываться при выполнении циклов ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО и ВВОД С ВНЕШНЕГО УСТРОЙСТВА соответственно.

Формирование сигналов шины управления поясним, пользуясь табл. 6.3.

Таблица 6.3

|

Тип цикла или группы циклов |

Вырабатываемый сигнал DBIN или WR |

Используемый разряд |

Уровень напряжения на выхо дах триггеров D29 микросхемы |

Вырабаты- ваемый сигнал шины управ- ления |

|||

|

9 |

1 |

16 |

10 |

||||

|

ЧТЕНИЕ |

DBIN |

D7 |

Н |

Н |

L |

L |

R, RW |

|

ЗАПИСЬ |

WR |

D4 |

L |

Н |

L |

L |

W, RW |

|

ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО |

WR |

D4 |

L |

L |

Н |

L |

OUT |

|

вводе ВНЕШНЕГО УСТРОЙ- СТВА |

DBIN |

D6 |

L H |

|

L |

H |

IN |

Рис. 6.10. Временная диаграмма циклов чтения и записи с переходом в режим ожидания:

а - цикл чтения; б - цикл записи

Для формирования сигнала R естественно воспользоваться разрядом D7 управляющего слова, так как именно в этом разряде имеется сигнал высокого уровня в циклах группы ЧТЕНИЕ (см. табл. 6.2), а для формирования сигналов OUT и IN — разрядами D4 и D6, потому что именно в этих разрядах сигнал имеет высокий уровень при выполнении соответствующих циклов и низкий уровень во всех остальных циклах.

Сложнее дело обстоит с формированием сигнала W для циклов группы

ЗАПИСЬ. Казалось, было бы естественно воспользоваться разрядом D1 управляющего слова, в котором передается сигнал низкого уровня для циклов группы ЗАПИСЬ. Но в этом разряде сигнал низкого уровня бывает также и в цикле ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО, и так как в этом цикле также вырабатывается сигнал WR, то пришлось бы усложнять схему, чтобы сформировать два разных сигнала W и OUT. Поэтому для формирования сигнала W используется инвертированный разряд D4. Соответствующий ему сигнал снимается с инверсного выхода триггера (вывод 7). Этот сигнал имеет высокий уровень и для циклов группы ЧТЕНИЕ и ВВОД С ВНЕШНЕГО УСТРОЙСТВА (см. табл. 6.2), но при этом не формируются сигналы W и OUT (так как не в ырабатывается сигнал WR), а формируются лишь сигналы R и IN (так как вырабатывается сигнал DBIN).

Сигнал высокого уровня RW формируется из сигнала R или W и управляет работой дешифратора адреса (см. § 7.2). В заключение опишем еще некоторые управляющие сигналы микропроцессора КР580ИК80А и их функции.

Вход READY используется для того, чтобы удлинить циклы ввода и вывода информации в микропроцессор и обеспечить таким образом возможность его работы с менее быстродействующими устройствами. Если во время высокого уровня сигнала Ф2 в такте Т2 какого-либо цикла на вход READY подается высокий уровень, то происходит нормальный цикл ввода или вывода информации. Если же подается низкий уровень, то микропроцессор с этого момента прекращает свою работу, сохраняя на всех выходах имеющиеся уровни сигналов (рис. 6.10). Такой режим называется режимом ожидания. Микропроцессор сигнализирует о том, что он находится в режиме ожидания, выработкой сигнала WAIT высокого уровня. В режиме ожидания микропроцессор не выполняет никаких операций и может находиться как угодно долго — до тех пор, пока не будет подан сигнал READY высокого уровня. После этого он завершает начатую операцию и продолжает далее свою работу.

Вход RESET используется для начального запуска микропроцессора и для повторных перезапусков. При подаче высокого уровня на этот вход микропроцессор прекращает свою работу, помещает во все разряды счетчика команд нули и бездействует до тех пор, пока на входе RESET остается высокий уровень. Как только высокий уровень снимается, он начинает выполнять команду, расположенную в ячейке памяти с нулевым адресом.

6.4. ТАКТОВЫЙ ГЕНЕРАТОР

И СХЕМА ПОШАГОВОГО ИСПОЛНЕНИЯ ПРОГРАММ

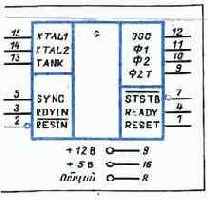

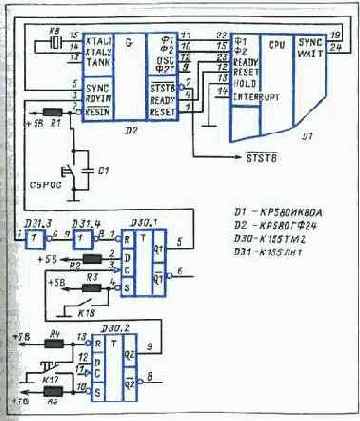

Для того чтобы получить тактовые импульсы с необходимыми для микропроцессора КР580ИК80А параметрами (см. § 6.2, рис. 6.2), можно использовать микросхему КР580ГФ24 (рис. 6.11, табл. 6.4). Эта микросхема является тактовым генератором, специально сконструированным для данного микропроцессора, и выполняет еще ряд дополнительных функций.

Т а б л и ц а 6.4

|

Название |

Назначение вывода |

|

XTAL1 XTAL2 |

Выводы для подключения кварцевого резонатора |

|

TANK |

Вывод, используемый при применении кварцевого резонатора с обертоном |

|

OSC |

Выход для синусоидального сигнала с частотой кварцевого резонатора |

|

Ф1.Ф2 |

Выходы для тактовых импульсов |

|

Ф2Т |

Выход для тактовых импульсов Ф2, но ТТЛ-уровня |

|

SYNC |

Вход для сигнала SYNC микропроцессора |

|

STSTB |

Выход для синхронизированного сигнала SYNC |

|

- |

Вход для асинхронного сигнала сброса |

|

RESIN |

|

|

RESET |

Выход для синхронизированного сигнала RESET микропроцессора |

|

RDYIN |

Вход для асинхронного сигнала готовности |

|

READY |

Выход для синхронизированного сигнала READY микропроцессора |

Рис. 6.12. Временные диаграммы синхронизации сигналов при помощи КР580ГФ24:

а - сигнал RESET; б - сигнал READY; в - сигнал SYNC

Опишем более подробно функции выводов тактового генератора. Выводы XTAL1 и XTAL2 предназначены для подключения кварцевого резонатора для стабилизации частоты генератора. При этом частота тактовых импульсов Ф1 иФ2 равняется 1/9 частоты кварцевого резонатора (так, в ПМ-ЭВМ при резонаторе на частоту 9 МГц частота тактовых импульсов равна 1 МГц).

На выходах Ф1 и Ф2 вырабатываются тактовые импульсы, удовлетворяющие всем предъявляемым для микропроцессора КП580ИК80А требованиям. На выходе OSC вырабатывается синусоидальный сигнал с частотой, которую имеет кварцевый резонатор. Все оставшиеся выводы (т. е. кроме Ф1, Ф2 и OSC) работают с сигналами, имеющими ТТЛ-уровни. На выходе Ф2Т вырабатывается сигнал, идентичный Ф2, но имеющий ТТЛ-уровень, который может быть использован для синхронизации каких-либо устройств в микро-ЭВМ.

Рис. 6.13. Схема подключения тактового генератора к микропроцессору

Три входа SYNC, RESIN, RDYIN являются входами для асинхронных сигналов. Эти сигналы могут менять свой уровень в любой момент времени. Внутри КР580ГФ24 с помощью специальных схем из этих сигналов формируются три выходных сигнала STSTB, RESET, READY, синхронизированных с тактовыми импульсами (рис. 6.12).

Тактовый генератор подключается к микропроцессору, как показано на рис. 6.13. К входу RESIN подключена кнопка СБРОС. Параллельно кнопке СБРОС подключен конденсатор С1, Если эта кнопка не нажата, то конденсатор С1 заряжен и на вход HESIN поступает высокий уровень. Следовательно, на вход RESET микропроцессора поступает низкий уровень, что позволяет ему нормально работать. Если нажать кнопку СБРОС, то на вход RESET поступит высокий уровень и работа микропроцессора будет прервана (см. § 6.3). Конденсатор С1 служит для начального запуска микропроцессора после включения питания. После включения питания С1 разряжен и на вход RESIN поступает низкий уровень. Затем конденсатор заряжается, напряжение на входе RESIN экспоненциально возрастает и в какой-то момент времени достигает высокого уровня. Это приводит к выработке сигнала RESET низкого уровня, разрешающего работу микропроцессора. Вход RESIN имеет специальную схему (триггер Шмидта), которая перерабатывает медленно меняющийся при заряде конденсатора входной сигнал в нормальный ТТЛ-фронт.

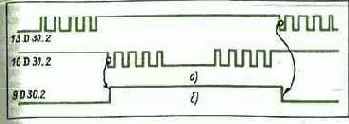

ПМ-ЭВМ можно снабдить схемой пошагового выполнения программы (рис. 6.13), построенной на микросхеме К155ТМ2 (D30) и двух инверторах (D31.3, D31.4).

С помощью этой схемы выполнение программы приостанавливается в середине каждого машинного цикла. Состояния шины данных в этот момент можно наблюдать на индикаторах одного из портов вывода (см. §7.3).

Схема пошагового выполнения программы работает следующим образом. Если контакты выключателя К18 замкнуты, то на вход 4 триггера D30.1 подается низкий уровень. На вход 1 также подается низкий уровень с выхода WAIT через буфер, состоящий из двух инверторов. В результате этого на выходе 5 триггера имеется высокий уровень, который, поступая на вход RDYIN, обеспечивает сигнал READY высокого уровня, что позволяет микропроцессору работать в нормальном режиме. Для перехода в режим пошагового выполнения программы необходимо разомкнуть контакты выключателя К18. Тогда на входе 4 триггера D30.1 будет высокий уровень, а на входе 1 — низкий уровень. Это приведет к тому, что на выходе 5 появится низкий уровень и микропроцессор перейдет в режим ожидания. После перехода в режим ожидания на выходе WAIT и на входе 1 триггера установится высокий уровень. В этом состоянии схема может находиться неограниченно долго. Если теперь подать на вход 3 триггера D30.1 фронт, то на выходе 5 появится высокий уровень. Микропроцессор снимет сигнал WAIT высокого уровня, закончит начатый машинный цикл и начнет выполнять следующий машинный цикл. Сигнал WAIT низкого уровня вновь установит на выходе 5 триггера низкий уровень, что приведет к переходу микропроцессора в режим ожидания в середине следующего машинного цикла.

Рис. 6.14. Явление дребезга контактов:

а - реальная временная диаграмма, дребезг контактов; б - идеальная временная диаграмма

Для подачи импульсов на вход 3 триггера D30.1 используются кнопка К17 и схема для подавления дребезга контактов. Явление дребезга контактов происходит при замыкании любых механических контактов вследствие неидеальности их поверхности. Вместо однократного замыкания или размыкания контакты замыкаются и размыкаются несколько раз.Так, при нажатии на кнопку К17 на выводах 13, 10 микросхемы D30.2 сигнал имеет форму, изображенную на рис. 6.i4. Чтобы сформировать сигнал, имеющий один срез, используется кнопка с двумя контактами: замыкающимся и размыкающимся при нажатии на нее. Когда один из контактов кнопки, соединенный с входами 10 и 13 микросхемы D30.2, замыкается, то первый из возникающих импульсов перебрасывает триггер, а остальные импульсы уже не влияют на его состояние. Таким образом, на выходе 9 формируются фронт при нажатии на кнопку К17 и срез при отпускании этой кнопки.

7