Микросхема АЦП К572ПВ1 является универсальным

|

Тип микросхемы |

Назначение |

Разрядность, бит |

Время преобразования, МКС |

Потребляемая мощность, Вт |

Тип корпуса |

Дифференциальная нелинейность, % |

Примечание |

|

К572ПВ1А |

АЦП |

12 |

150 170 |

0,09 |

4134.48 — 2 |

+0,05 |

U1BHx=2,4 В, |

|

К572ПВ1Б |

АЦП |

12 |

150 170 |

0,09 |

4134.48 — 2 |

+0,1 |

|

|

К572ПВ1В |

АЦП |

12 |

150... 170 |

0,09 |

4134.48 — 2 |

±0,2 |

У«вых=0,3 В |

|

К594ПА1 |

ЦАП |

12 |

3,5 |

0,5 |

405.24 — 2 |

±0,024 |

__ |

|

КРП00СК2 |

УВХ |

— |

tв = 5, txР = 50 |

0,06 |

201.14 — 1 |

0,1 |

Схр=1000 пф, 4=100 не |

|

К1107ПВ1 |

АЦП |

6 |

0,1 |

1,0 |

2207.48 — 1 |

+ (0,5-0.8) |

U1вых=2,4 В, |

|

К1107ПВ2 |

АЦП |

8 |

0,1 |

2,5 |

2136.64 — 1 |

±(0,2-0,4) |

U°вых=0,4 В |

|

К1107ПВЗА |

АЦП |

6 |

0,01 |

1,0 |

201.16 — 13 |

±(0,5+0,8) |

U1вых=—(1,1.-0,7) В, |

|

КП07ПВЗБ |

АЦП |

6 |

0,02 |

1,0 |

201.16 — 13 |

±(0,5+0,8) |

U0вых= — (2...1.5) В |

|

КП08ПВ1 |

АЦП |

10 |

1,0 |

0,8 |

210Б.25 — 1 |

±(0,1+0,4) |

U1Bых=2,4 В, U0вых=0,4 В |

|

КП08ПА1А |

ЦАП |

12 |

0,4 |

0,8 |

2105.24 — 1 |

±0,024 |

U1Bx>2,0 В, |

|

КП08ПА1Б |

ЦАП |

12 |

0,7 |

0,8 |

2105.24 — 1 |

±0,024 |

U°вх<0,8 В |

|

КШЗПВ1А |

АЦП |

10 |

30 |

0,35 |

238.18 — 1 |

+0,1 |

U°вых=0,4 В, |

|

КШЗПВ1Б |

АЦП |

1П |

30 |

0,35 |

238.18 — 1 |

±0,2 |

У1вых=2,4 В |

|

КШЗПВ1В |

АЦП |

10 |

30 |

0,35 |

238.18 — 1 |

±0,4 |

Микросхема К111ЗПВ1 представляет собой функционально полный узел АЦП, предназначенный для использования в блоках аналогового ввода. Для включения микросхемы необходимы два источника питания и несколько резисторов. Наличие выходных буферных регистров с тремя состояниями позволяет непосредственно подключить микросхему к шине данных МП.

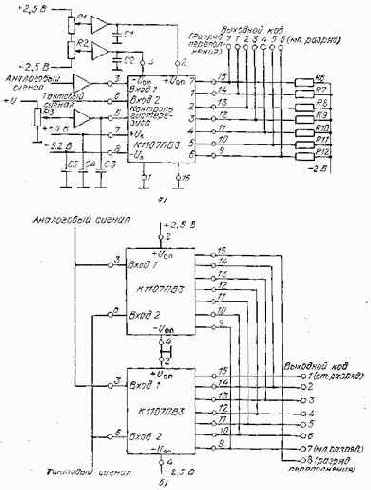

Структуры, типовые схемы включения и особенности эксплуатации приведенных в табл. 1.6 преобразователей рассмотрены в [22]. Исключение сос тавляет АЦП К1107ПВЗ. Рассмотрим его подробнее [24]. Быстродействующие шестиразрядяые преобразователи К1107ПВЗА,Б позволяют осуществлять преобразование напряжения в диапазоне ±2,5 В с максимальной частотой 100 и 50 МГц (для преобразователей с индексами А и Б соответственно).

Преобразователь построен по параллельной схеме, следовательно, при выборке аналоговый сигнал поступает одновременно на 64 компаратора. Особенностью построения преобразователя является отсутствие выходного регистра. Это приводит к тому, что часть периода «тактирования» цифровой код на выходе не определен. Длительность этого периода равна длительности режима выборки, но по времени сдвинута относительно его начала.

Типовая схема включения АЦП приведена на рис. 1.8. .Выходы микросхемы через резисторы R6 — R12 сопротивлением 100 Ом подключены к источнику напряжения — 2 В. Два источника опорного напряжения ( + 2,5 В и — 2,5 В) через калибровочные резисторы Rl, R2 подключены к выводам 2 и 4. Для повышения стабильности работы микросхемы на высокой частоте предусмотрена подача на вывод 5 регулируемого напряжения, предназначенного для управления гистерезисом компараторов. Напряжение регулируется от О до 2 В. В основном микросхема применяется без внешнего напряжения гистерезиса. Нестабильность опорных и питающих напряжений вызывает появление дополнительных погрешностей. Для ослабления влияния колебаний напряжений источников к ним подключаются блокировочные конденсаторы С1 — С5 емкостью 0,1 мкФ. АЦП КП07ПВЗ содержат разряд переполнения (вывод 15). Наличие такого разряда позволяет увеличить разрядность преобразователя путем пар ал дельного объединения микросхем (рис... 1.8,6). Для высокочастотных сигналов печатные проводники представляют собой микрополоековые линии. Для исключения отражений сигналов в этих линиях и обеспечения максимального быстродействия АЦП его выводы необходимо согласовать с трактом.

Для этой цели в микросхеме предусмотрены отдельные выводы 16; «Цифровая земля» и 1 «Аналоговая земля», которые подключаются к соответствующим шинам, причем соединение шин осуществляется только в одной точке — на клемме источника питания.

Рис. 1.8. Типовая схема включения микросхемы АЦП К1107ПВЗ (а) и способ объединения двух микросхем (б)

Ограниченные размеры кристалла и невысокая точность изготовления элементов полупроводниковых микросхем обуславливают использование, наряду с полупроводниковыми, АЦП и ЦАП, выполненных по тонкопленочной технологии. В [53] описан АЦП повышенного быстродействия, выполненный по тонкопленочной технологии с использованием бескорпусных микросхем. Преобразователь построен по последовательно-параллельной конвейерной схеме и имеет следующие характеристики: разрядность выходного кода 10, период дискретизации 350 не, амплитуда входного сигнала + 2,5 В, апертурное время 0,2 не, дифференциальная нелинейность 0,2%, потребляемая мощность 20 Вт.

Микросхема УВХ КРП00СК2 реализована на кристалле с размерами 1,7X2,1 мм. Значительное время выборки (5 мке) ограничивает область применения этого устройства узкополосными сигналами. Более быстродействующие УВХ выполняются обычно либо в виде ГИС, либо в виде функционального узла с дискретными элементами. Примеры таких УВХ рассмотрены в [23].

Способы обмена информацией между АЦП и МП. Обмен информацией между периферийными устройствами (включая АЦП) и МП называют вводом-выводом, а устройства, выполняющие эту процедуру, — устройствами ввода-вывода.

Операция ввода информации включает три шага: МП выставляет адрес АЦП на шину адреса; МП ждет, когда УВВ выставит Данные на шину данных; МП считывает данные и помещает их в °дин из регистров.

Операция вывода информации также включает три шага: МП выставляет адрес ЦАП; после получения сигнала о том, что ЦАП готов к приему данных, МП выставляет данные на шину данных; МП ждет завершения передачи данных.

Для согласования работы МП и АЦП используются различные способы обмена информацией. Выбор конкретного способа определяется типом МП, скоростью обмена, сложностью и структурой массива данных и т. п. Специализированные МПУ, используемые в РЭА, производят обмен информацией с УВВ, которые в зависимости от конкретного применения имеют (различные характеристики. Например, для системы передачи телеметрической информации характерно большое число информационных каналов и невысокая скорость их опроса. Для МПУ обработки сигналов — ограниченное число каналов и высокая скорость обмена информацией. Исходя из этих особенностей, коротко рассмотрим следующие способы обмена информацией МП с УВВ: программно-управляемую передачу данных; обращение к УВВ как к ячейке памяти; прерывание и прямой доступ к памяти. Подробнее описание этих способов приведено в [10, 13, 19].

При использования программно-управляемой передачи данных система команд МП должна содержать специальные команды ввода-вывода. Обман данными между МП и УВВ осуществляется в следующей последовательности:

1. МП выдает на адресную магистраль адрес УВВ.

2. МП осуществляет проверку состояния готовности УВВ к обмену информацией. Эта процедура может выполняться, например, с помощью триггера — флага. Если этот триггер находится в состоянии 1, то происходит переход к п. 3. Если триггер — в состоянии 0, то МП повторяет команду опроса состояния УВВ либо осуществляет переход к другому устройству.

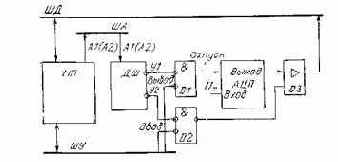

3. МП осуществляет ввод или вывод данных. Такая последовательность программно-управляемой передачи данных характерна для АЦП, работающих независимо от МП. Если АЦП запускается одновременно с приемом от МП своего адреса, то вместо опроса состояния триггера можно ввести программную задержку, равную циклу работы АЦП. По истечении времени задержки МП осуществляет ввод или вывод данных. Структурная схема программно-управляемой передачи данных от АЦП в МП приведена на рис. 1.9 [25].

Микропроцессор выдает в шину адреса ад рес ПУ А1. Этот адрес поступает на дешифратор ДШ, который в соответствии с принятым кодом адреса формирует управляющий сигнал У1, поступающий на вентиль D1. На второй вход вентиля с шины управления поступает сигнал «Вывод». При совпадении сигналов «Вывод» и VI на выходе D1 формируется сигнал запуска АЦП. Затем МП переходит в режим ожидания, длительность которого определяется временем преобразования АЦП. По окончании программной задержки МП выдает в адресную шину адрес А2, а в шину управления — «Ввод». Микросхема D2 формирует сигнал, по которому цифровые данные с выхода АЦП через магистральный усилитель D3 поступают на ШД и вводятся в МП.

Рис. 1.9. Структурная схема подключения АЦП к микропроцессору с использованием программно-управляемой передачи данных

Итак, реализация программно-управляемого ввода-вывода не требует затрат адресов памяти и относительно проста. Основным недостатком этого способа обмена информацией является затраты времени на ожидание готовности ЦАП или АЦП к выдаче или приему данных. Близким к рассмотренному выше способу обмена информацией является обращение к УВВ как к ячейке памяти. В этом способе УВВ рассматривается как ячейка памяти. Микропроцессор использует одни и те же команды для обмена как с памятью, так и с УВВ. Конкретное УВВ определяется только своим адресом. Отличиями обращения к УВВ как к ячейке памяти являются: отсутствие особых команд ввода-вывода, УВВ требуют выделения им некоторого числа адресов.

Основным недостатком рассмотренных выше способов обмена информацией является потеря процессорного времени на ожидание готовности УВВ к обмену. Для устранения этого недостатка используется способ обмена информацией с прерыванием программы, выполняемой МП. Прерывание программы может происходить по инициативе УВВ. Для этого оно посылает в МП сигнал «Запрос прерывания», который поступает на специальный вход. Число входов запросов на прерывание колеблется от S1 до 8 для различных МП.

На каждый вход могут поступать сигналы запросов на прерывание более чем от одного источника (такие сигналы могут объединяться по ИЛИ).

После приема сигнала «Запрос на прерывание» МП приостанавливает вычисления по основной программе и переходит к выполнению подпрограммы обмена информацией с УВВ. Эта подпрограмма содержит ряд процедур, подробное описание которых рассмотрено в [10, 13]. После выполнения подпрограммы обмена информацией МП продолжает выполнение основной программы.

Примеры построения (различных схем прерывания с использованием микросхем векторного приоритетного прерывания Ат2914, расширителя приоритетного прерывания Ат2913, а также других БИС серии Ат2900 приведены в [5].

В рассмотренных выше способах обмен информацией осуществляется между УВВ и МП. Для ввода-вывода данных в ОЗУ, минуя МП, используется способ обмена информацией с помощью прямого доступа к памяти (ПДП). Организация обмена данными в режиме ПДП осуществляется обычно контроллером ПДП. Микропроцессор передает управление шинами контроллеру ПДП, который производит обмен данными непосредственно между памятью и УВВ; ПДП может быть реализован таким образом, чтобы выполнять пересылки данных между различными блоками памяти или разными УВВ, использующими общую с МП шину. При этом значительно повышается скорость обмена данными, которая определяется временем доступа к памяти.

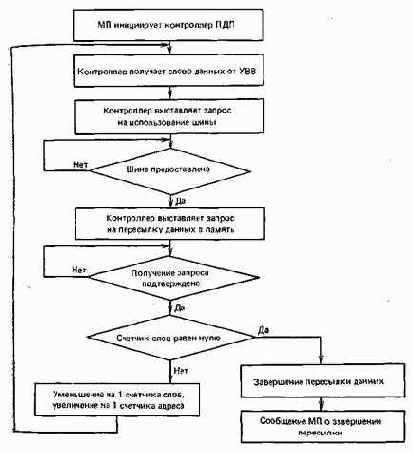

Рис. 1.10. Структурная схема алгоритма операции ввода по методу прямого доступа к памяти

Устройства ввода-вывода и МП для связи с памятью пользуются одной шиной и, следовательно, не могут обращаться к памяти в одном цикле. Существуют несколько -вариантов реализации ПДП, в том числе: с блокировкой МП, с квантованием цикла памяти и захватом цикла [13]. В первом варианте — на время пересылки данных контроллер ПДП останавливает МП .и отключает его от шины. Недостатками ПДП с блокировкой МП являются затраты времени на отключение МП от шины и последующее его подключение, а также потеря процессорного времени во время пересылки.

При ПДП с квантованием цикла памяти используется быстродействующая память, цикл которой делится на два временных интервала, причем один из них отводится для МП, а другой — для ПДП. Этот метод позволяет достичь максимальной скорости обмена данными при параллельном выполнении операций » МП. Недостатком метода является необходимость применения быстродействующей памяти, которая потребляет большую мощность и имеет большую стоимость.

Компромиссным вариантом между быстродействием и стоимостью ПДП является метод захвата цикла. При этом методе контроллер ПДП отнимает у МП цикл памяти для пересылки данных. В процессе выполнения обмена данными с УВВ МП не блокируются. Если цикл памяти нужен одновременно МП и контроллеру ПДП, то приоритет отдается ПДП. Таким образом, производительность МП снижается только в тех ситуациях, когда цикл работы МП близок к циклу памяти. Использование микропрограммного управления при построении МПУ приводит к тому, что цикл выполнения команды значительно больше цикла памяти. Это позволяет МП и контроллеру ПДП обращаться к памяти практически без взаимных помех. При работе нескольких МП с общей памятью увеличивается число обращений к последней и поэтому производительность ПДП снижается.

При организации пересылки данных между УВВ и памятью, контроллер ПДП должен выполнять ряд функций. На рис. 1.10 приведена схема алгоритма операции ввода при ПДП. Микропроцессор инициирует работу контроллера ПДП подачей на него команды ввода, начального адреса памяти, отведенной для массива данных, числа слов вводимого массива и другой информации, необходимой для выполнения операции. Затем контроллер получает от УВВ слово данных и запрашивает разрешение на использование шины МПУ для пересылки с ПДП. После предоставления шины контроллер запрашивает разрешение на пересылку данных в память. Получив от памяти сигнал подтверждения о том, что текущий цикл обмена с памятью завершен, контроллер ПДП анализирует содержимое счетчика слов, которое равно числу слов пересылаемого массива данных.

Если содержимое счетчика слов не Равно нулю, то оно уменьшается на единицу, а содержимое счетчика адреса памяти увеличивается на единицу. После этого осуществляется прием (следующего слова данных. Загрузка массива в память продолжается до тех пор, пока значение счетчика слов не становится нулевым. При этом контроллер ПДП прекращает пересылку данных и информирует МП о том, что пересылка завершена.

Обычно контроллеры ПДП представляют собой достаточно сложные устройства и содержат несколько десятков микросхем средней степени интеграции. Уменьшения числа микросхем можно достичь путем использования специальных БИС МПК, реализующих функции контроллера ПДП, например контроллер ПДП серии К588, БИС генератора адреса ПДП Ат2940 и др.

Использование когаюретого способа сопряжения ПУ и МП является одним из важнейших вопросов проектирования МПУ, применяемых в РЭА. Он должен решаться с учетом вычислительных возможностей МП, структуры построения МПУ, разрядности и размерности массива данных, требуемой скорости обмена, обеспечивающей РМВ обработки сигналов, и других требований.

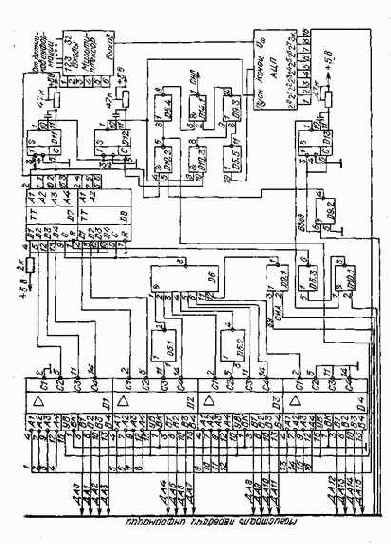

Рис. 1.11. Схема подключения АЦП к микропроцессору

В качестве примера рассмотрим устройство сопряжения АЦП с МП, приведенным иа рис. 1.4 [26].

Пример 1.4. Иа рис. 1.11 приведена схема устройства сопряжения АЦП с МП, интерфейс которого совместим с интерфейсом микро-ЭВМ «Электрони-ка-60». Устройство сопряжения включает: четыре магистральных приемопередатчика (Dl — D4), реализованных на микросхемах К589АП26; дешифратор адреса на микросхемах К155ЛН1 (D5.1, D5.2) и К155ЛА2 (D6); адресный регистр К155ТМ8 (D7, D8); два одновибратора К.155АП (Dll, D12); схему управления режимами работы магистральных приемопередатчиков D10, D9, D14, реализованную на микросхемах К155ЛАЗ, К155ЛЕ1, К155ЛА8 соответственно. Для установки адресного регистра в исходное состояние используются микросхемы D10.1, D9, D13.

Для ввода информации с АЦП МП формирует адрес УВВ и выставляет его на шину данных — адреса (ДА).

Кроме адреса МП выдает также сигналы обращения к внешнему устройству (ВУ) и синхронизации активного устройства (СИА). Эти сигналы вместе с иодом адреса (АО — А15) поступают на дешифратор адреса (D5, D6), который вырабатывает сигнал стробирования для запоминания младших разрядов адреса в адресном регистре D7, D8. С выхода регистра D7, D8 код адреса поступает на мультиплексор, который выбирает соответствующий адресу датчик информации и подключает его ко входу АЦП. Одновременно с выдачей адреса на мультиплексор запускаются одновибраторы Dll, D12, которые используются для формирования задержки запуска АЦП на время срабатывания мультиплексора и для выработки сигнала «Пуск». Микропроцессор вырабатывает сигнал «Ввод», означающий его готовность к приему данных от АЦП. По приему этого сигнала и наличию сигнала «Пуск» на выходе микросхемы D10.2 формируется сигнал переключения магистральных приемопередатчиков на передачу. После приема сигнала «Ввод» устройство сопряжения вырабатывает сигнал «СИП» и выставляет данные на шину ДА. Задержка формирования сигнала «СИП» не должна превышать для данной схемы 10 мкс. Если в течение этого времени сигнал «СИП» не выработан устройством, то МП выходит на прерывание. С учетом этих требований ввод информации в МП в течение одного цикла возможен в том случае, если АЦП имеет время преобразования не более 5 мкс, мультиплексор — время переключения не более 3 мкс. При выполнении этих требований организация операции ввода информации сводится к выполнению одной команды пересылки.

Данное устройство реализовано в виде функциональной ячейки микро-ЭВМ (габаритные размеры печатной платы 143X252x12 мм). АЦП типа Ф7077/1,. мультиплексор реализован на микросхемах серии К591.