Этапы разработки ССИС

Приведем некоторые данные из программы разработки сверхскоростных БИС (ССИС) на основе МОП-приборов (табл. 2.4) [36].

Теоретически сокращение размеров в n раз приведет к повышению плотности компоновки в п2 раз. Однако из-за того, что с ростом числа элементов на кристалле растет и площадь соединений, плотность компоновки максимально повышается только в m раз (m<n2). Пропорционально с сокращением линейных размеров элементов в n раз уменьшаются значения токов и напряжений, а потребляемая мощность уменьшается в п2 раз.

Принципиальный недостаток сокращения размеров элементов -состоит в том, что в п2 раз повышается сопротивление соединений, что приводит к повышению плотности тока в n раз. Это может привести к миграции атомов металла проводника и другим вредным эффектам, снижающим надежность.

Наряду с повышением качества МП БИС, существенной проблемой улучшения конструкций МПУ является сокращение площади монтажных плат, занимаемой соединениями. Суть проблемы заключается в том, что с ростом степени интеграции площадь соединений на кристалле или подложке превышает площадь, занимаемую активными элементами. Наряду с этим, в [37, 38] показано, что без проведения оптимизации соединений в БИС процесс повышения степени интеграции практически будет приостановлен вследствие достижения логическими элементами своих физических пределов.

Повышение эффективности использования площади БИС и .подложек связано с решением задач совершенствования размещения элементов и трассировки связей на кристалле и подложке; оптимизации структурных и схемотехнических методов построения логических элементов в кристалле и БИС на монтажных платах.

Проблема оптимизации соединений свойственна конструкциям БИС, микросборок и ФЯ, тем более что для ряда устройств (например, ИЦП) эти конструкции близки.

Рассмотрим некоторые пути повышения эффективности использования плошади кристалла БИС. Полученные результаты во многом справедливы и для перспективных конструкций МПУ,

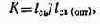

Для оценки качества размещения элементов и трассировки связей на кристалле БИС используют коэффициент оптимизации «связи К:

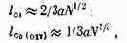

где Lcb, 1св(опт) — средняя длина линий связи при произвольном и оптимальном размещении элементов соответственно. В [37] показано, что

где N — число логических элементов на кристалле или степень интеграции; а — усредненный шаг размещения элементов на кри-сталле;

(SKp — площадь кристалла БИС). Подставив (2.8) в (2.7), получим

В табл. 2.5 приведены значения К для различной степени ин-теграции БИС.

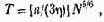

Из табл. 2.5 видно, что с ростом степени интеграции N увели-чивается длина монтажных линий связи. Поэтому при конструи--ровании БИС и СБИС необходимо предусмотреть достаточную плошадь кристалла для выполнения межэлементных связей. Вели-чина этой площади зависит, в основном, от числа соединительных трасс или трассировочной способности кристалла БИС (Т):

где n — усредненная нагрузочная способность логического эле-мента, численно равная среднему числу входов логического эле-мента; n — коэффициент заполнения трасс кристалла; обычно среднее значение n = 0,5 — 0,7. Считая типовым случаем n = 0,5, a n = 3, получаем T = 2N5/6.

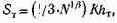

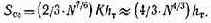

Площадь кристалла БИС для реализации межэлементных связей:

где ST — плошадь одной трассы. Для случая произвольного раз-мещения логических элементов при а= 1

где ят — шаг трасс.

Подставляя (2.10) в (2.9), получаем

Как видно из (2.11), с ростом степени интеграции увеличивается доля площади кристалла, отводимая под соединения между логическими элементами. Для. уменьшения этой площади необходимо повышать: качество размещения элементов на кристалле БИС, разрешающую способность технологии изготовления, число-слоев межэлементных соединений. Однако эти направления не смогут решить проблему роста площади соединений, поскольку имеют свои пределы.