МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА В РАДИОЭЛЕКТРОННОЙ АППАРАТУРЕ

ОСОБЕННОСТИ ПРИМЕНЕНИЯ И КОНСТРУИРОВАНИЯ ВСТРАИВАЕМЫХ В РЭА МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

2.1. ОБЛАСТИ ПРИМЕНЕНИЯ КОНСТРУКТИВНО ВСТРОЕННЫХ В РЭА МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

Развитие современной РЭА характеризуется широким применением цифровых -методов обработки, преобразования и регистрации сигналов. Устройства, входные и выходные сигналы которых представляются в цифровой форме, называют цифровыми. Элементной базой таких устройств являются цифровые ИМС различной степени интеграции.

Прогресс в области микроэлектроники привел к созданию микропроцессорных БИС, являющихся элементной базой построения нового класса цифровой РЭА — микропроцессорных устройств (МПУ), которые представляют собой функционально законченные, программно управляемые вычислительные устройства.

Чаще всего МПУ применяются совместно с цифровыми устройствами (жесткой логикой), расширяя функциональные возможности РЭА. Радиоэлектронные устройства (РЭУ) объединяют аналоговые, цифровые и аналого-цифровые узлы. Конструкция такого устройства обычно представляет собой моноблок [27]; МПУ, реализующие некоторые функциональные узлы РЭУ, встраиваются в него и конструктивно представляют собой одну или несколько функциональных ячеек моноблока |[28].

Области применения МПУ в современной РЭА определяются, в основном, их быстродействием и функциональными возможностями по сравнению с комбинационными устройствами. По мере изменения этого соотношения в пользу МПУ расширяются и области их применения. Исходя из современного уровня функциональных возможностей МПУ, можно выделить следующие области применения микропроцессоров в РЭА.

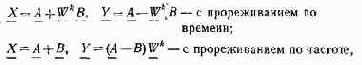

Цифровые системы радиосвязи. В цифровых системах радиосвязи находят применение широкополосные шумоподобные модулирующие сигналы. Использование таких сигналов позволяет рас-

средоточить энергию излучаемого сигнала в широком диапазоне частот, определяемом шириной спектра модулирующего сигнала. Рассмотрим пример использования микропроцессоров при построении таких систем [29].

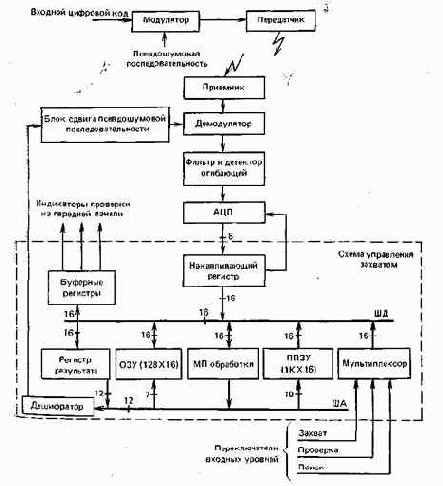

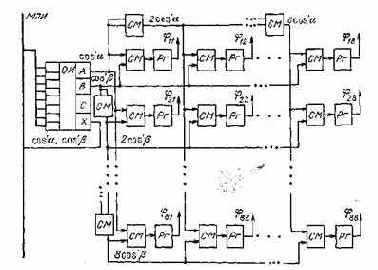

Пример 2.1. Упрощенная структурная схема цифровой системы радиосвязи с широкополосными шумоподобными сигналами изображена на рис. 2.1. В данной системе связи низкочастотный входной цифровой сигнал модулируется высокочастотной псевдошумовой последовательностью. Ширина спектра промодулированного сигнала увеличивается пропорционально длине псевдослучайной последовательности. Такое расширение спектра позволяет рассредоточить энергию сигнала в широком диапазоне частот, что повышает отношение сигнал-шум при узкополосных помехах. Для демодуляции входного сигнала необходимо в приемном устройстве создать опорную псевдослучайную последовательность, идентичную модулирующей. После вычитания псевдослучайной последовательности из входного сигнала в высокочастотном демодуляторе-смесителе на выходе приемного устройства появляется исходный цифровой код данных.

Рис. 2.1. Структурная схема цифровой системы радиосвязи

Основной задачей схемы управления захватом, выполненной на базе микропроцессора СР-1600, является обеспечение и поддержание синхронизма друг относительно друга двух псевдошумовых последовательностей: принимаемой и опорной. На выходе детектора огибающей уровень сигнала будет нарастать пропорционально значению функции корреляции между двумя псевдошумовымв последовательностями. Этот сигнал, преобразованный в цифровую форму и усредненный по времени наблюдения, поступает на микропроцессор обработки, который работает в трех режимах: захват, проверка, поиск. Порог сравнения, соответствующий принятому режиму работы, устанавливается переключателем, входных уровней и через мультиплексор поступает в ОЗУ.

Программируемое ПЗУ емкостью 1КХ16 предназначено для хранения программ обработки входного сигнала. Код рассогласования, вырабатываемый микропроцессором обработки, поступает на регистр результата и буферные регистры. В соответствии с принятым кодом рассогласования дешифратор вырабатывает управляющее напряжение, которое осуществляет сдвиг псевдошумовой последовательности с целью получения максимальных значений напряжения на выходе детектора огибающей.

Точность синхронизации не превышает 1 бита. Микропроцессорная реализация схемы управления захватом обеспечивает выполнение трех режимов работы системы на одной и той же аппаратуре, возможность оперативного изменения длительности псевдослучайной последовательности и, следовательно, повышение помехоустойчивости системы связи.

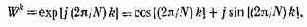

Цифровая обработка сигналов (включая цифровую фильтрацию, спектральный анализ, корреляционную обработку и т. п.). Алгоритмы цифровой обработки сигналов основываются на вычислении операции свертки. Для вычисления операции свертки применяется, в основном, прямое и обратное дискретное преобразование Фурье (ДПФ). Для линейных дискретных систем с постоянными параметрами, к классу которых относятся цифровые устройства обработки сигналов, прямое и обратное ДПФ -может быть представлено в матричной форме [2]:

где Хn, Xk — матрицы-столбцы сигнала и его спектра размером. N; Fkn — унитарная матрица базисных функций размером NxN; F*kn — матрица, комплексно-сопряженная Fhn-

Для вычисления ДПФ в соответствии с (2.1) необходимо выполнить (N — I)2 умножений и N (N — 1) сложений комплексных чисел. Для уменьшения числа операций умножения и сложения

при вычислении ДПФ в практике проектирования цифровых устройств обработки сигналов используется алгоритм быстрого преобразования Фурье (БПФ) и его модификации [30].

Суть алгоритма БПФ заключается в том, что когда размер матрицы Fkn является составным числом, то матрица может быть представлена в виде произведения слабозаполненных матриц, т. е. факторизована. Это дает возможность производить вычисления ДПФ в несколько этапов, выполняя на каждом из них лишь небольшое число операций. Благодаря этому достигается экономия вычислений. Если N = rL, то г называют основанием преобразования, a L — числом этапов преобразования.

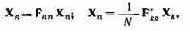

При цифровой обработке радиотехнических сигналов в качестве базисных функций чаще всего используются дискретные экспоненциальные функции вида

где Wh — дискретная экспоненциальная функция или поворачивающий коэффициент; iV — размер матрицы-столбца сигналов.

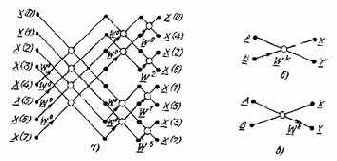

На рис. 2.2 изображен граф 8-точечного БПФ по основанию 2 с прореживанием по времени. Незачерченные кружочки обозначают операции сложения — вычитания, причем верхний выход означает сумму, нижний — разность. Стрелкой обозначена операция умножения на поворачивающий коэффициент. На графе можно выделить элементарный подграф базовой операции (при г = 2 это БПФ двух отчетов). Базовую операцию можно представить следующим образом:

причем X, У, А, В, Wh — комплексные числа.

Рис. 2.2 Граф 8-точечного быстрого преобразования Фурье (БПФ) (а)- базовые операции алгоритма БПФ с прореживанием по времени (б) и по частоте (в)

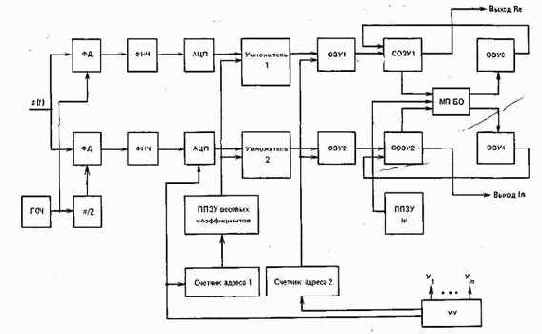

Блоки СОЗУ1, СОЗУ2 выполняют функции внутрипроцессорного интерфейса. На его вход поступают отсчеты входного сигнала с ОЗУ1, ОЗУ2 на первом этапе вычисления БПФ и промежуточные отсчеты с ОЗУЗ, ОЗУ4 назера-Бесселя [2]. Умножитель может быть реализован на БИС параллельных умножителей КР1802ВРЗ — КР1802ВР5. Максимально допустимое время умножения ty одного отсчета должно быть не больше, периода дискретизации Tn — 1JAF. Если Tд=(2-3) мкс, то целесообразно использовать 8-разрядный последовательный умножитель К.Р1802ВР2, потребляемая мощность которого ниже, либо умножитель К588ВР2, выполненный по КМОП-технологии.

«Взвешенные» отсчеты входного сигнала поступают на ОЗУ1 и ОЗУ2, емкость памяти которых определяется размерностью входного массива N:N= =Tc/Ta, где Tc — длительность обрабатываемого сигнала.

Сигналы, считанные из ОЗУ, поступают из вход МП БПФ, включающего сверхоперативные ОЗУ — СОЗУ1, СОЗУ2, МП БО, ППЗУ поворачивающих коэффициентов и выходные ОЗУЗ, ОЗУ4, остальных L — 1 этапах вычисления БПФ. С выхода СОЗУ отсчеты сигнала поступают на вход МП БО.

После вычисления ВПФ действительные и мнимые значения спектральных составляющих записаны в ОЗУЗ, ОЗУ4 соответственно. При приходе управляющих сигналов считывания эти значения через СОЗУ1, СОЗУ2 поступают на выход; СОЗУ1, СОЗУ2 npoVro реализуются на БИС обмена информации КР1802ВВ1.

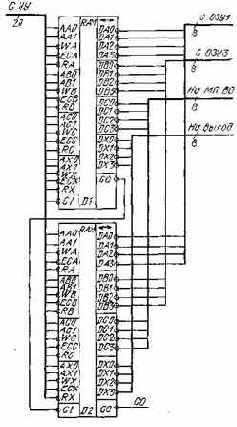

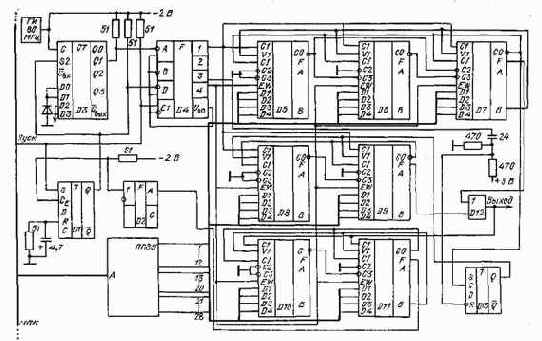

Пример такой реализации для 8- разрядных магистралей показан на рис. 2.6. Разрешением обмена информации с каналами А, В, С, X управляют входы ЕСА, ЕСВ, ЕСС, ЕСХ. Выбор режима работы (считывание — запись) определяется сигналами RA, RB, RC, RX; WA, WB, WC, WX соответственно при разрешении обмена информацией с выбранным каналом. Входные сигналы ААО, АА1, АВО; АВ1, АСО, АС1, АХО, АХ1 обеспечивают выбор одного из четырех внутренних регистров БИС. Архитектура БИС ОИ обеспечивает помодульное наращивание разрядности выходных магистралей DA, DB, DC, DX. Магистрали DA, DB, DC предназначены для работы на короткие линии связи. Магистраль DX может работать на длинные согласованные линии связи (в данном случае выходные).

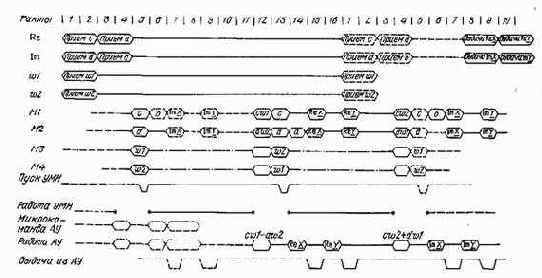

Рис. 2.4. Временная диаграмма работы микропроцессора базовой операции алгоритма быстрого преобразования Фурье

Рис. 2.5. Структурная схема вычислителя быстрого преобразования Фурье

Рис. 2.6. Функциональная схема СОЗУ, выполненного на БИС КР1802ВВ1

Используя МП БО и МП БПФ, можно построить различные цифровые устройства обработки сигналов.

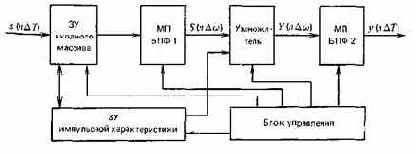

Пример 2.4. Сигнал на выходе цифрового фильтра равен дискретной свертке входного сигнала s(nAT) с импульсной характеристикой системы h[nAT): y(nAT)=s(nДT)+h(nДT), где + — операция дискретной свертки. Известно, что свертка во временной области соответствует умножению в частотной области [30]. В соответствии с (2.1) получаем

Рис. 2.7. Структурная схема цифрового фильтра

На рис. 2.7 приведена структурная схема фильтра, реализующего алгоритм (2.3) и построенного на базе МП БПФ (см. рис. 2.5). Микропроцессор БПФ1 выполняет задачу спектрального анализа, т. е. переводит временной сигнал s(nAT) в частотную область. Далее вычисляется спектр выходного сигнала: Y(nAw). Микропроцессор БПФ2 выполняет обратное ДПФ, т. е. переводит сигнал из частотной области во временную. Как следует из (2.3), для реализации прямого и обратного ДПФ необходимы одинаковые функциональные блоки.

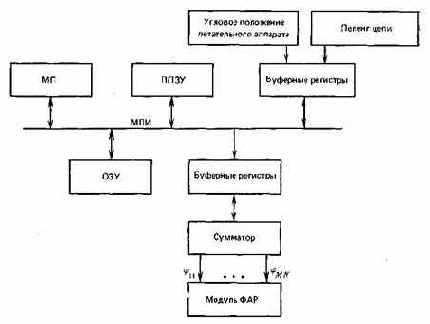

Рис. 2.8. Структурная схема адаптивного цифрового фильтра

Если вместо ЗУ импульсной характеристики использовать микропроцессор, вычисляющий ее значения, то получим адаптивный фильтр. Применяются такие фильтры при селекции движущихся целей на фоне отражений от поверхности Земли и метеобразований. Поскольку реальная окружающая среда отличается от предполагаемой, которая закладывалась в ЗУ импульсной характеристики, то характеристики реального синтезированного фильтра отличаются от оптимальных, что вносит потери. Эти потери можно скомпенсировать, если адаптивно реагировать на изменение окружающей среды. Структурная схемэ адаптивного фильтра изображена на рис. 2.8. Этот фильтр аналогичен фильтру, изображенному на рис. 2.7, за исключением того, что значения импульсной характеристики периодически пересчитываются в зависимости от окружающей обстановки.

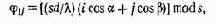

Управление лучом фазированной антенной решетки (ФАР) бортовой РЛС. Алгоритм управления лучом ФАР бортовой РЛС включает две части. Одна из них предназначена для вычисления направляющих косинусов по данным углового положения летательного аппарата в пространстве и предварительному указанию пеленга цели: (sd/Л)cos а и (sd/Л)cos$, где s — число состояний фазотаращателя; s = 2п/Дф (Дф — дискрет .приращения фазы); X — длина волны. Вторая часть алгоритма позволяет по полученным значениям направляющих косинусов рассчитать фазовое распределение в ФАР ![27]:

где (fij — значение фазы; ij — номер столбца и строки ФАР соответственно; (fa]mods — символ операции взятия целой части числа ПО МОДУЛЮ 5.

Анализ алгоритмов управления лучом ФАР показывает, что его первая часть содержит более 50% различных тригонометрических преобразований. Вычисление тригонометрических функ-

ций обычно осуществляется приближенными методами, использующими их разложение в ряд Маклорена. Вторая часть алгоритма, как следует из (2.4), по сути, (сводится к многократному повторению операции сложения, причем число операций сложения определяется размерностью модуля ФАР и равно псл = МхМ% М и N — число строк и столбцов ФАР соответственно.

Реализация такого количества сложений на МП, последовательно вычисляющем фij для каждого излучателя, привела бы к большим временным затратам. Поэтому целесообразно вычислитель управления лучом ФАР реализовать на МП с использованием аппаратного-сумматора, реализующего алгоритм (2.4).

Пример 2.5. Структурная схема вычислителя управления лучом ФАР приведена на рис. 2.9. Данные об угловом положении летательного аппарата и предварительное значение пеленга цели поступают через буферные регистры » ОЗУ. Микропроцессор в соответствии с программой, хранимой в ППЗУ, вычисляет значения направляющих косинусов для данного положения ЛА. Эти значения через буферные регистры подаются на сумматор, вычисляющий значения фазового распределения согласно (2.4). Структурная схема матричного сумматора для ФАР 8X8 приведена на рис. 2.10. Значения направляющих косинусов и сигналы управления поступают на буферный регистр, выполненный на БИС КР1802ВВ1, и далее на матричный сумматор, который вычисляет значения фij для каждого излучателя. Вычисленные значения хранятся в регистрах, а по сигналу считывания они поступают на фазовращатели ФАР. Общее время вычисления фазового распределения зависит от быстродействия сумматоров и приблизительно равно 9tсл.

Рис. 2.9. Структурная схема вычислителя управления лучом фазированной антенной решетки

Рис. 2.10. Структурная схема матричного сумматора 8X8

Комбинационные схемы. Микропроцессоры применяются для замены комбинационных схем, выполненных на ИМС средней и малой степени интеграции. Такие схемы в РТУ выполняют функции блоков синхронизации, .кодирующих и декодирующих устройств, устройств управления и т. п. Цифровые автоматы реализуются в основном на -матричных МП БИС типа ППЗУ и ПЛМ; при этом используются классические методы теории конечных автоматов. Методы синтеза конечных автоматов достаточно подробно освещены в .литературе. В [1] описывается система автоматизированного синтеза автоматов на матричных БИС.

Эта сис тема предназначена для синтеза автоматов, поведение которых описано граф-схемами алгоритмов (ГСА), в качестве элементной базы используются ПЛМ, ППЗУ, регистры, дешифраторы. При синтезе автоматов на этой системе необходимо учитывать следующие ограничения: общее число вершин ГСА не более 1023, число различных микрокоманд в ГСА не более 511, число различных микроопераций в ГСА не более 127, число внутренних состояний автомата не более 1023. Из приведенных данных видно, что сложность синтезируемых автоматов ограничивается несколькими тысячами внутренних состояний. При построении более сложных автоматов используются МП БИС совместно с комбинационными схемами. Типовой пример такого применения МП БИС приведен в [31]. Рассмотрим его подробнее.

Рис. 2.11. Функциональная схема программируемого синхронизирующего устройства

Пример 2.6. Функциональная схема программируемого синхронизирующего устройства приведена на рис. 2.11. Устройство выполнено на БИС К589ХЛ4 и представляет собой многофункциональное синхронизирующее устройство (D5 — D11).

В устройстве можно выделить следующие основные узлы: схему формирователя импульсов (D1 — D4), схему временной задержки (D5 — D7) и формирования частоты следования импульсов (D8, D9), формирователь числа импульсов в пакете (D10 — D11).

Схема формирования импульсов выполнена на микросхемах К500ТМ131 (D1), К500ПУ124 (D2), К500ИЕ136 (D3) и К500ПУ125 (D4). Устройство запускается подачей импульса «Пуск», а также управляющих и адресных сигналов на ППЗУ, поступающих с магистрали передачи информации (МПИ). При приходе сигнала «Пуск» триггер D1 устанавливается в 1; этот сигнал поступает на счетчик. Счетчик D3 работает в режиме деления частоты входных импульсов 80 МГц на 4, что достигается подачей кода ООП на его входы DO — D3. Неопределенность начала появления импульсов относительно сигнала «Пуск» не превышает периода следования импульсов кварцевого генератора 12,5 не.

Полученная последовательность ЭСЛ-уровня преобразуется в ТТЛ-уровень микросхемой D4.

С выхода D4 импульсы поступают на схему временной задержки. Выходной импульс длительностью 25 не появится на выходе F D7 через время задержки, определяемое из выражения Кп=2п — (t3 — tH)f, где t3 — время задержки; Кп — код пересчета (на входах D микросхем D5 — D7); тя и f — длительность и частота входных импульсов.

С выхода СО D7 положительный перепад напряжения устанавливает триггер D13 в 1, разрешая этим прием импульсов с f=20 МГц на схему формирования частоты следования импульсов (D8, D9). В зависимости от кода пересчета Кп, подаваемого на входы D микросхем D8, D9 изменяется частота следования импульсов, снимаемых с выхода F D9, по следующему закону: Кп = 2п — Kд, где Ад — коэффициент деления устройства.

Формирователь числа импульсов в пакете собран на элементах D10, D11. На его вход поступают выходные сигналы с D12. Число импульсов в пакете N определяется из выражения Кп=2n — (N — 1). После подсчета N импульсов на выходе F D11 появится сигнал, который своим фронтом через D2 установит триггер D1 в 0. При этом счетчик D3 перейдет в режим загрузки и работа всей схемы остановится.

Выбор необходимой задержки, частоты следования и длительности пакета импульсов определяется управляющим 28-разрядным кодом, считываемым из ППЗУ, по адресу, поступающему от микропроцессора с МПИ. Данное устройство позволяет устанавливать временную задержку 50 не — 204,8 мке, период следования импульсов 50 не — 12,3 мке, число импульсов в пакете 3 — 256. Устройство может применяться для управления работой АЦП, МП БО и др.

2.2. ОСОБЕННОСТИ ПРИМЕНЕНИЯ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ В РЭА

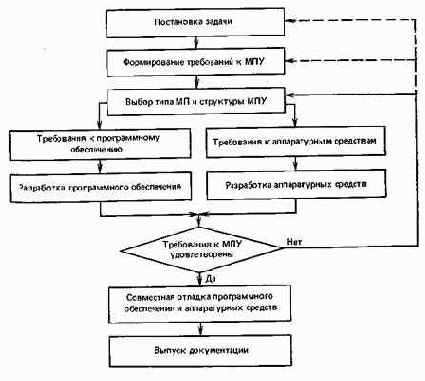

При проектировании РЭА на МП БИС, в отличие от комбинационных цифровых устройств необходима совместная разработка программного обеспечения и аппаратных средств. Основные этапы проектирования МПУ приведены на рис. 2.12.

На этапе постановки задачи определяются входные и выходные требования к МПУ, математические методы решения поставленной задачи, разрабатываются алгоритмы решения задачи и взаимодействия МПУ с РЭУ.

Анализируя алгоритмы, решаемые МПУ и РЭУ, формируются требования и ограничения на их реализацию. Эти этапы являются типичными для любого РЭУ и поэтому обычно не вызывают затруднений.

Рис. 2.12. Основные этапы проектирования микропроцессорных устройств

На последующих этапах процесс проектирования раздваивается на аппаратурную и программную части. Первый же этап: выбор типа МП и структуры МПУ требует от специалиста знаний элементной базы МПУ, их систем команд, имеющегося программного обеспечения, средств отладки и т. п. На основе этих знаний осуществляется разбиение структуры МПУ на аппаратурную и программную части. Далее, исходя из выбранной структуры МПУ, конкретизируются требования к программному обеспечению и аппаратурным средствам. Осуществляется предварительная разработка программы и аппаратуры. Оцениваются основные характеристики МЛУ. Эти характеристики сравниваются с требованиями, предъявляемыми к МЛУ. Если полученные характеристики являются удовлетворительными, то осуществляется совместная отладка программного обеспечения и аппаратурных средств. По результатам отладки выпускается техническая документация.

Если характеристики не удовлетворяют требованиям, предъявляемым к МЛУ, выбирается другой МП или изменяется структура МПУ и весь процесс проектирования повторяется. Если для всего имеющегося в распоряжении разработчика набора МП и допустимых структур построения МЛУ не будет найдено удовлетворительное решение, то необходимо изменить требования, предъявляемые (К МПУ. Это достигается либо выбором более эффективных математических методов и алгоритмов, либо перераспределением задач между РЭУ и МЛУ.

В книге основное внимание будет уделено следующим этапам: выбору типа МП и структуры МПУ, предварительной разработки программного обеспечения и аппаратных средств, определению характеристик МЛУ. Этапы постановки задачи и формирования требований к разрабатываемым устройствам подробно изложены в специальной литературе, например [30, 32].

Отладка программного обеспечения рассмотрена в [9 — 11].

Кроме разработки программного обеспечения можно выделить еще ряд особенностей применения МПУ в РЭА: реальный масштаб времени обработки сигналов, использование аппаратных микропроцессоров, разработка специальных периферийных устройств и интерфейсных схем.

Реальный масштаб времени обработки сигналов (РМВ). Под РМВ обработки сигналов понимается необходимость обеспечения временного ограничения на выполнение алгоритма обработки сигналов: Тпр<Т, где Тпр — время выполнения программы микропроцессором; Т — допустимое время выполнения программы. Значение Гпр зависит от выполняемого алгоритма обработки, типа МП, его системы команд, структуры и т. п. Значение Т определяется структурой и требованиями к РЭУ, параметрами обрабатываемого сигнала. Для различных РЭУ и сигналов Т определяется по-разному. Рассмотрим, как определяется Т для МЛ БПФ (см. рис. 2.5).

Пример 2.7. Пусть МП БПФ решает задачу спектрального анализа сигнала, имеющего следующие параметры: полоса анализируемых частот AF= = 100 кГц, длительность обрабатываемого сигнала Гс = 10 мс. Требуется определить Т для МП БПФ и МП БО.

Для обеспечения РМВ необходимо, чтобы допустимое время спектрального анализа T<TCl т. е. время выполнения программы БПФ МП должно быть не более 10 мс. Частота дискретизации (при использовании квадратурных каналов) Fa=AF — l00 кГц. Размерность обрабатываемого массива N=2AFTC = =2-103. Число выполняемых БО NBQ=N/2*log2N=ll 103. Допустимое время выполнения одной БО ТБО <0,9 мкс. Микропроцессор БО (см. рис. 2.3) не обеспечивает решение данной задачи в РМВ. Поэтому необходимо использовать в МП БО вместо двух — четыре умножителя, либо в МП БПФ использовать несколько МП БО.

Допустимое время согласованной фильтрации более чем в 2 раза меньше-времени спектрального анализа, так как включает вычисление обратного ДПФ л умножение на импульсную характеристику. Параметр Т для МП управления лучом ФАР (см.

рис. 2.9) определяется максимально допустимым временем обнаружения цели T0: Т<Т0. Для других применений МП в РЭА Т определяется по-иному.

Использование аппаратных микропроцессоров. Для большинст ва задач обработки сигналов быстродействие микропроцессорных вычислителей недостаточно. Необходимо построение многомикропроцессорных систем. В |[2, 33] приведены примеры таких систем.

Существенное повышение быстродействия МПУ может дать применение аппаратных микропроцессоров, реализующих наиболее сложные, с вычислительной точки зрения, участки алгоритма обработки. Так, использование матричного сумматора в вычислителе управления лучом ФАР (пример 2.5) позволяет осуществить расчет фазового распределения за время, приблизительно равное 9tсл.

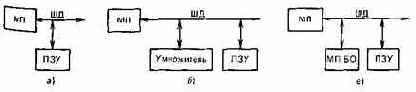

Возможны различные структурные варианты использования аппаратных микропроцессоров совместно с программными, некоторые из них приведены на рис. 2.13. В [2] приведены программы, реализации алгоритмов БО и БПФ для МП серий КР580, К589. В табл. 2.2 представлены данные о числе операций, используемых в алгоритмах, и времени вычисления этих операций.

Из табл. 2.2 видно, что умножение занимает значительную часть времени вычисления БО. Использование умножителей КР1802ВРЗ для вычисления БО позволяет снизить время ее вычисления для МП КР580 до 3082 мкс, для К589 до 20,4 мкс, для КР1802 до 1,5 мкс.

Рис. 2.13. Структурные схемы подключения аппаратных микропроцессоров к программным:

а — микропроцессор выполняет базовую операцию по программе, хранимой в ПЗУ; б — операция умножения выполняется аппаратно; в — базовая операция выполняется аппаратно